GLASSMAN HIGH VOLTAGE, INC. Route 22 East, Salem Industrial Park Whitehouse Station, NJ 08889

> Our Glassman is a Model SP/WG-10N30 SN M348220-02BC900718

> > INSTRUCTION MANUAL

WG SERIES

Mode1 PS/WG-10N30

Serial M308480-05

Date /- 22-90

Issue #3 Effective from April 22, 1985

# TABLE OF CONTENTS

# WG SERIES

| Warrant | /User Registration Card                                 | i   |

|---------|---------------------------------------------------------|-----|

| SECTION | I GENERAL DESCRIPTION AND<br>PERFORMANCE SPECIFICATIONS | 1.0 |

| Α.      | Features and Applications                               | 1.1 |

| В.      | Design Features                                         | 1.2 |

| с.      | Rating Charts                                           | 1.3 |

| D.      | Options                                                 | 1.3 |

| E.      | Simplified Theory of Operation                          | 1.3 |

| F.      | Electrical Specifications                               | 1.4 |

| G.      | Mechanical Specifications                               | 1.4 |

| SECTION | II APPLICATIONS INFORMATION                             | 2.0 |

| Α.      | Unpacking and Inspection                                | 2.1 |

| В.      | Installation and Operation                              | 2.2 |

| с.      | Polarity Reversal                                       | 2.4 |

| D.      | Remote Control Connections and Applications             | 2.4 |

| Ε.      | Correspondence and Ordering Spare Parts                 | 2.7 |

# TABLE OF CONTENTS (Cont'd.)

| SEC | TIO | ON III THEORY OF OPERATION                                                              | 3.0  |

|-----|-----|-----------------------------------------------------------------------------------------|------|

| L   | А.  | Main Assembly                                                                           | 3.1  |

| ]   | в.  | High Voltage Assembly                                                                   | 3.2  |

| ſ   | с.  | Transformer Primary, and Power Transistor<br>Collector Drive Circuitry                  | 3.4  |

| ]   | D.  | Bias Voltages                                                                           | 3.6  |

|     | Ε.  | Voltage Feedback Input Amplifier,<br>Polarity Reversal, and Voltage<br>Monitor Circuits | 3.7  |

|     | F.  | Current Feedback Input Amplifier,<br>Polarity Reversal, and Current<br>Monitor Circuits | 3.8  |

|     | G.  | Feedback Control Amplifiers and<br>Programming, Voltage and Current<br>Regulators       | 3.10 |

|     | H.  | Pulse Width Modulator                                                                   | 3.11 |

|     | I.  | Protection and Other Miscellaneous<br>Circuits                                          | 3.12 |

|     |     | 1. External Interlock                                                                   | 3.12 |

|     |     | 2. Slow Start Circuit                                                                   | 3.12 |

|     |     | 3. SCR Cutoff Protection Circuits                                                       | 3.12 |

|     |     | 4. Mode Indicating Lights                                                               | 3.13 |

|     |     | 5. AC Line Overvoltage                                                                  | 3.14 |

# SECTION II - APPLICATIONS INFORMATION

# THIS EQUIPMENT EMPLOYS VOLTAGES THAT ARE

DANGEROUS. EXTREME CAUTION MUST BE EXERCISED

# WHEN WORKING WITH THIS EQUIPMENT

# A. Unpacking and Inspection

First inspect package exterior(s) for evidence of rough handling in transit. If none, proceed to unpack... carefully. After removing the supply from its shipping container(s), remove the top dust cover(s) and inspect thoroughly for damage. In some models the high voltage assembly is shipped in its own container and should also be thoroughly inspected.

#### IMPORTANT

In cases of damage due to rough handling in transit, notify the carrier immediately if damage is evident from appearance of package. Do not destroy or remove any of the packing material used in a damaged shipment. Carrier companies will usually not accept claims for damaged material unless they can inspect the damaged item and its associated packing material. Claims must be made promptly - certainly within five days of receipt of shipment.

Check out the power supply operation and performance as outlined below.

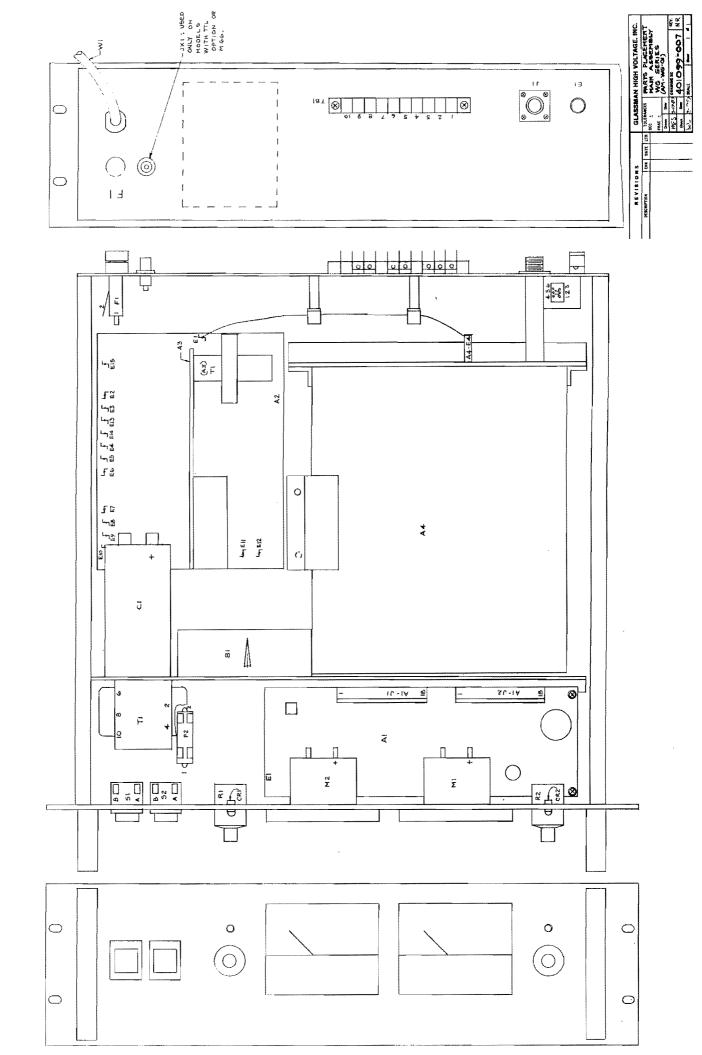

## B. Installation and Operation

The following procedure should be followed to connect and operate the equipment, after it has been placed or mounted in position.

#### WARNING

THIS EQUIPMENT EMPLOYS VOLTAGES THAT ARE DANGEROUS. EXTREME CAUTION MUST BE EXERCISED WHEN WORKING WITH THIS EQUIPMENT.

A 3-PRONG GROUNDED PLUG IS PROVIDED FOR CONNECTION TO AC LINE. IF A GROUNDED RECEPTACLE IS NOT AVAILABLE, USE AN ADAPTER AND CONNECT THE THIRD WIRE TO A GOOD GROUND -PREFERABLY A WATER SYSTEM GROUND.

ALWAYS MAKE CERTAIN THAT THE RETURN LINE FROM THE LOAD IS CONNECTED TO THE GROUND STUD AT THE REAR OF THE UNIT. A GOOD EXTERNAL WATER SYSTEM GROUND SHOULD ALSO BE CONNECTED TO THIS STUD.

- 1. Check the input voltage rating on the nameplate of the supply and make certain that this is the rating of the available power source.

- 2. Connect the input cable to the power source.

- 3. In models in which the high voltage assembly is physically not contained within the control assembly, interconnection cabling is provided and must be attached between the main control assembly and the high voltage assembly.

- a. For models with an output voltage of greater than 60kV, the high voltage assembly is contained in a polyethylene enclosure which is mounted in a separate 5-4" high rack chassis.

The control and high voltage assembly chassis are both  $5-\frac{1}{4}$ " high and are intended to be mounted one above the other to use  $10-\frac{1}{2}$ " of rack space. Normally the control chassis is mounted above the high voltage chassis, but this is arbitrary.

b. A control cable with circular connectors (plugs) on both ends is provided to interconnect between the control assembly and the high voltage assembly. The connectors mate with a receptacle on the rear of the control chassis and on the rear of the high voltage assembly chassis.

- c. Note that there is a "jumper" connection in the wires attached to the high voltage assembly chassis receptacle. This is an interlock connection which prevents the power supply from operating unless both connectors are plugged into their respective receptacles.

- d. A high voltage RF connection is also required between the control and high voltage assembly chassis. This is supplied in a short length with plugs on each end of the high voltage lead so that a short loop between the pair of corresponding high voltage receptacles on the rear of the chassis can be achieved. This wire carries high voltage AC (5kV peak) and should not make contact with any ground surfaces or other low voltage elements. It should be an "air borne" lead.

- 4. Connect the high voltage output cable and ground return lead to the load. Insert the high voltage output cable into the receptacle on the rear panel. Spring action should be felt as the probe reaches the bottom of the receptacle. Hold the cable pressed down against the spring as the locking nut is screwed onto the receptacle.

- 5. Rotate OUTPUT VOLTAGE control to fully counter-clockwise position. (This is optional, but desirable to prevent damage to external equipment caused by inadvertent overvoltage setting. Not required if correct setting has already been determined.)

- 6. Rotate OUTPUT CURRENT control to approximately midscale (a setting of 5 on the 10-turn control).

- Apply input power to the supply by depressing the POWER ON/OFF pushbutton. The indicator should light.

- 8. Energize high voltage by depressing the HV ON pushbutton. The indicator should light.

- 9. Rotate the OUTPUT VOLTAGE control clockwise and observe that both the voltmeter and the ammeter rise. The ammeter reading is a function of the load connected to the supply, and will not read if a load is not connected. The output end of the high voltage output cable, if connected to the supply, must be prevented from coming too close to ground, or high voltage breakdowns may occur.

- 10. The mode indicators on the front panel indicate whether the supply is operating in a voltage regulated or current regulated mode.

- 11. To shut down, press the POWER ON/OFF pushbutton.

# WARNING: DO NOT HANDLE THE LOAD UNTIL IT HAS BEEN DISCHARGED - CHECK KILOVOLTMETER!!! AN UNLOADED SUPPLY MAY TAKE UP TO 15 SECONDS TO FULLY DISCHARGE.

## C. Polarity Reversal

#### Models 60kV and below

For reversible polarity models 60kV and below, the power supply has been shipped with two high voltage assemblies, one positive and one negative. The serial label on the high voltage assembly indicates its polarity. To reverse the polarity of the power supply, it is necessary to interchange the high voltage modules. First remove the dust cover from the unit. Then remove the electrical connector that is mounted on the rear of the unit, noting where it is, so you will know how to replace it. Next, remove the assembly from its mechanical constraint. Install the other high voltage assembly by reversing your steps.

#### Models above 60kV

For reversible polarity models above 60kV, the power supply has been shipped with two high voltage chassis, one positive and one negative. The serial label on the rear of the chassis indicates its polarity. To reverse the polarity of the power supply, simply interchange the high voltage chassis.

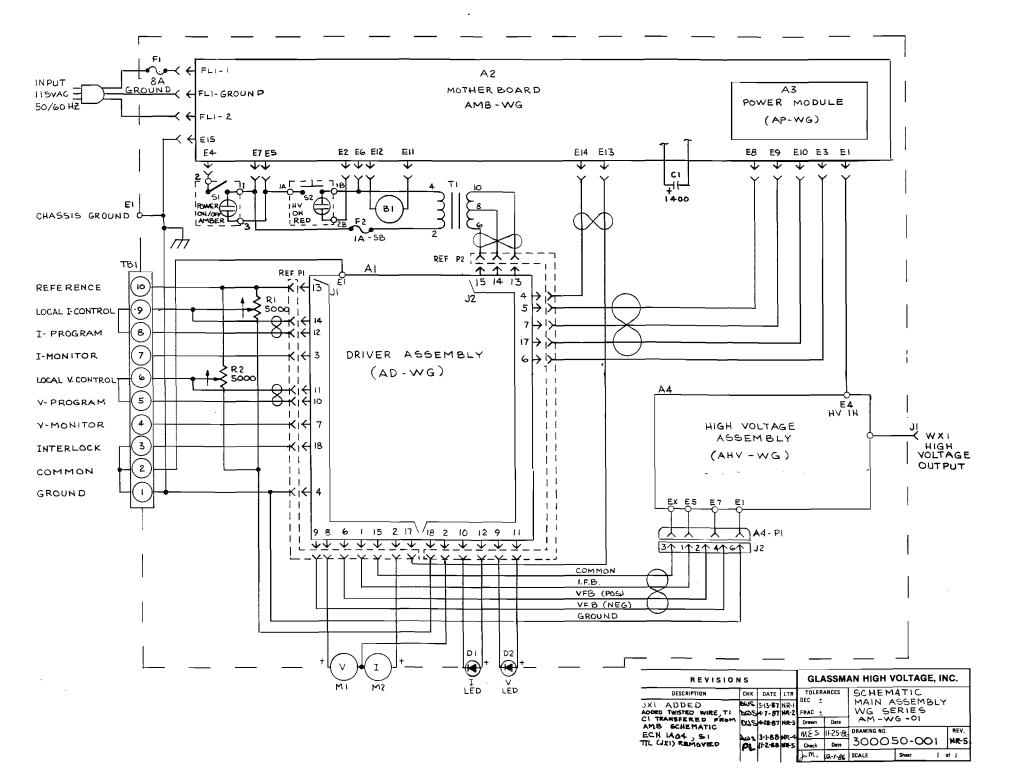

D. Remote Control Connections and Applications

Terminal board TB1 is mounted on the rear panel of the control chassis and has the following functions:

- TB1-1: Ground. This is an auxiliary instrumentation ground terminal. The main ground terminal is a "stud", El, located near the high voltage output connector.

- TB1-2: Common. This terminal is the instrumentation/ measurement circuit return. It is "DC" connected to ground, internally, by a pair of back-to-back diodes. If left floating, this point will clamp at approximately 500 millivolts. The power supply

is shipped from the factory with a barrier jumper across TB1-1 and TB1-2, so that, normally, the common is operated at ground potential. If desired, the user may lift this jumper and allow the common to "float". This may be done for the purpose of inserting a current monitoring circuit which will measure "true" load current, with no internal drain included in the measurement. When attempting this, it should be remembered that the inserted drop must not exceed the 500 millivolt clamping voltage, or erroneous readings will be obtained.\*

- TB1-3: External Interlock. This terminal must be connected to common, TB1-2, to enable the power supply control circuits. These terminals have been shorted by a barrier jumper terminal at the factory to assure start-up. When desired, the jumper may be removed and replaced by an external switch device which must be closed to make the supply operable. When the external switch is open, the power supply output will drop to zero. Consult GLASSMAN Engineering Department for alternate interlock configurations, such as TTL enable logic.

- TB1-4: Voltage Monitor. A 0-10 volt, positive with respect to common/ground, signal in direct proportion to output voltage is available at this terminal. A 10 K ohm limiting impedance protects the internal circuitry, so that a digital voltmeter with greater than 10 megohms input impedance should be used to monitor this terminal. It is also acceptable to use a 1 milliampere DC full scale instrument for monitor purposes.

- TB1-5: Voltage Program. To operate with remote voltage programming, first remove the barrier jumper between TB1-5 and TB1-6. A 0-10 volt, positive with respect to common/ground, signal will control the output from zero to rated voltage. The user may provide his own external programming control signal, or may use an external potentiometer across the reference to derive a programming voltage. The preferred value for an external potentiometer is 10 K ohms, although values from 5 K through 50 K ohms will be satisfactory. When inserting an external programming signal, the negative end should be connected to the common/ground terminal TB1-1/2. The positive end should be connected to terminal TB1-5.

When connecting an external potentiometer using the power supply internal reference, connect as follows:

Clockwise terminal to TB1-10 (reference voltage)

Counter-clockwise terminal to TB1-1/2 (common)

Slider terminal to TB1-5 (program input)

In this mode of operation, the front panel control serves as an overvoltage limit for the remote control. As an example, if the front panel control is set to 50%, then the remote control is capable of adjustment from 0 to 50% only, which corresponds to a signal voltage of 0 to 5 volts DC. If full range control is desired, the front panel control must be set to maximum. In any case, the power supply will "clamp" the programming input at the front panel control setting, and thereby protect against inadvertent overvoltage programming signals up to 50 volts DC.

- TB1-6: Local Voltage Control. This terminal is normally used as the voltage source for the voltage program input. As such, the power supply is shipped with a barrier jumper connecting TB1-5 and TB1-6. To operate with remote voltage programming, the jumper must be removed and proceed as described in TB1-5 above.

- TB1-7: Current Monitor. A 0-10 volt, positive with respect to common/ground, signal in direct proportion to output current is available at this terminal. Use an instrument with at least 10 megohm input impedance to monitor this terminal.

- TB1-8: Current Program. To operate with remote current programming, first remove the barrier jumper between TB1-8 and TB1-9. A 0-10 volt, positive with respect to common/ground, signal will control the output from zero to rated current. The user may provide his own external programming control signal, or may use an external potentiometer across the reference to derive a programming voltage. The preferred value for an external potentiometer is 10K ohms, although values from 5K through 50K ohms will be satisfactory.

When inserting an external programming signal, the negative end should be connected to the common/ ground terminal, TB1-1/2. The positive end should be connected to terminal TB1-8.

When connecting an external potentiometer using the power supply internal reference, connect as follows:

Clockwise terminal to TB1-10 (reference voltage)

Counter-clockwise terminal to TB1-1/2 (common)

Slider terminal to TB1-8 (program input)

In this mode of operation, the front panel current control serves as an overcurrent limit for the remote control. It works analogously to the overvoltage clamp action of the front panel voltage control as described in TB1-5 above.

- TB1-9: Local Current Control. This terminal is normally used as the voltage source for the current program input. As such, the power supply is shipped with a barrier jumper connecting TB1-8 and TB1-9. To operate with remote current programming, the jumper must be removed and proceed as described in TB1-8 above.

- TB1-10: Reference. An ultra-stable, 10 volt, positive with respect to common (terminal TB1-2), reference is supplied for user programming applications. Remember that the common is normally at ground potential, so that external circuitry may be returned directly to ground. Maximum current drain from this reference should be limited to 3 milliamperes to maintain normal operation, although no damage will be done even with a severe overload at this terminal.

- \* NOTE: When operating the power supply with jumper between common (TB1-2) and ground (TB1-1) removed, any equipment connected to the common terminal (TB1-2) must not be grounded.

# E. Correspondence and Ordering Spare Parts

- 1. Each Glassman power supply has an identification label on the rear of the chassis that bears its model and serial number.

- 2. When requesting engineering or applications information, reference should be made to this model and serial number, as well as to the component symbol number(s) shown on the applicable schematic diagram, if specific components or circuit sections are involved in the inquiry.

3. When ordering spare parts, the information described in Paragraph 2 should be given, in addition to the Glassman part number that appears on the parts list.

Examples: 1. When requesting engineering data:

"...voltage across capacitor C2, for serial no. M020670 of model PS/WG-30P10 power supply."

2. When requesting that component:

"...one (1) Glassman part no. CFH1-10.0-0.015 capacitor C2 for serial no. M020670 of model PS/WG-30P10 power supply."

#### SECTION III - THEORY OF OPERATION

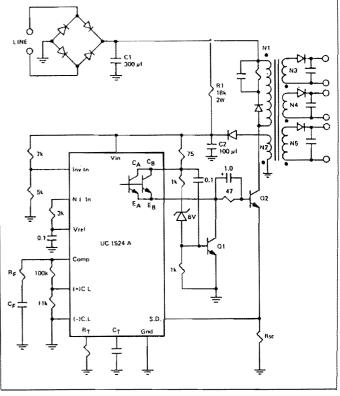

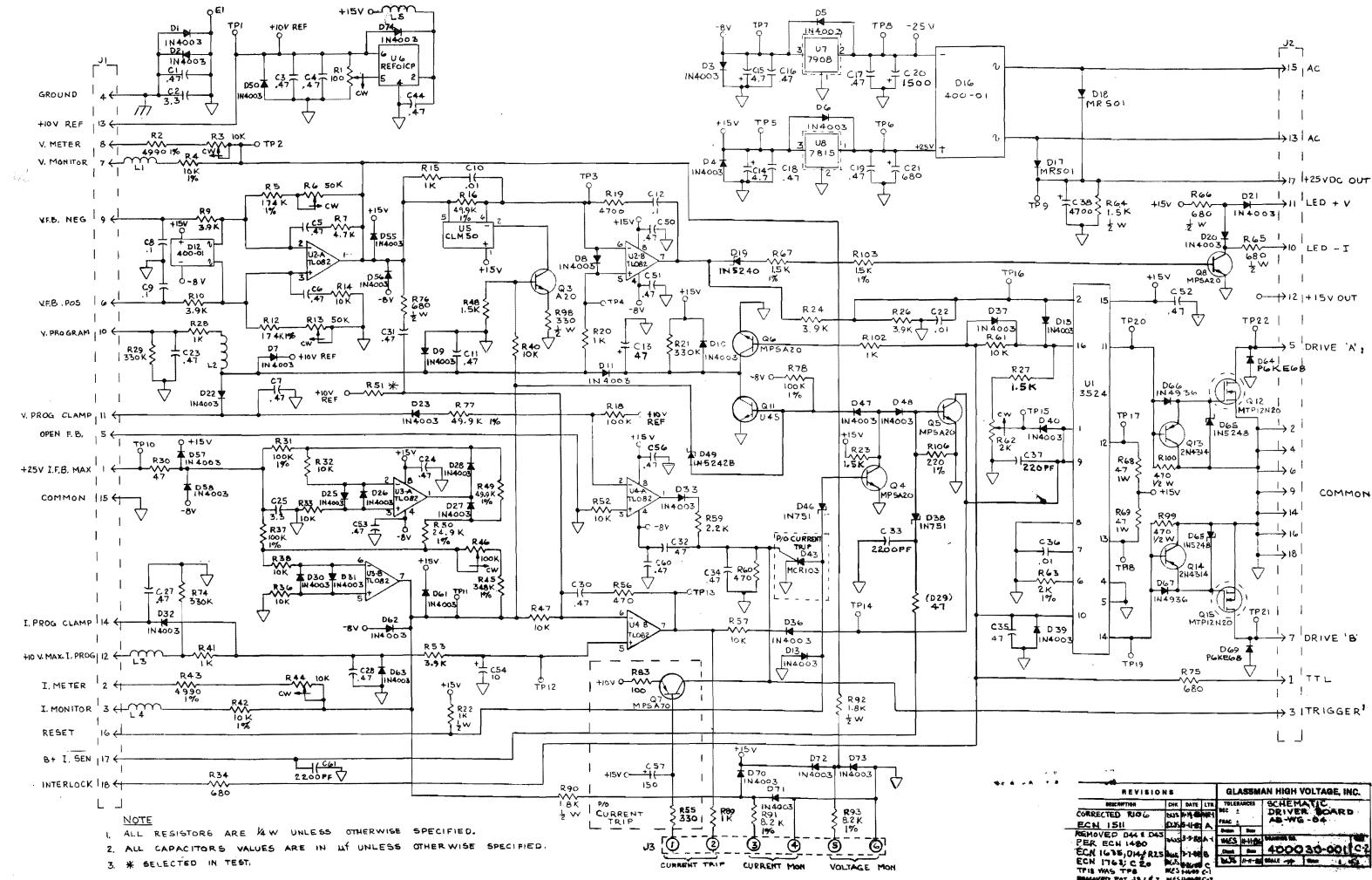

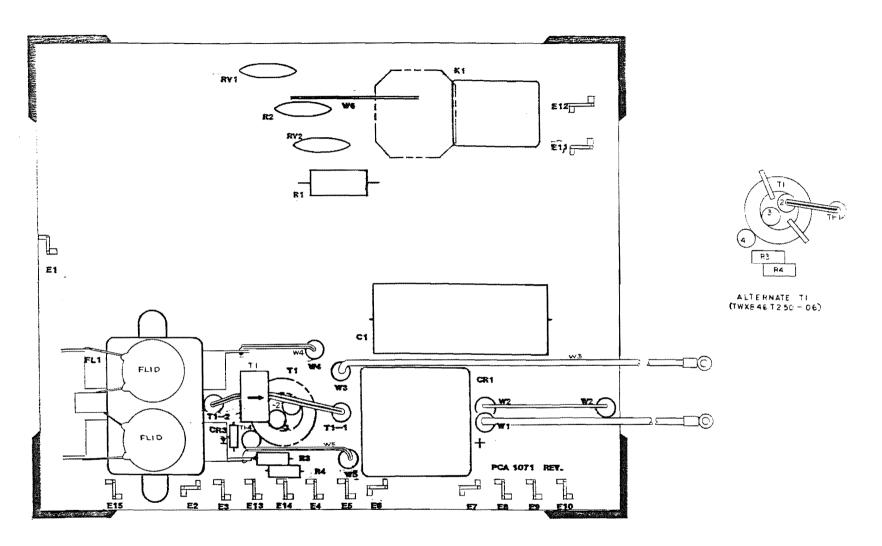

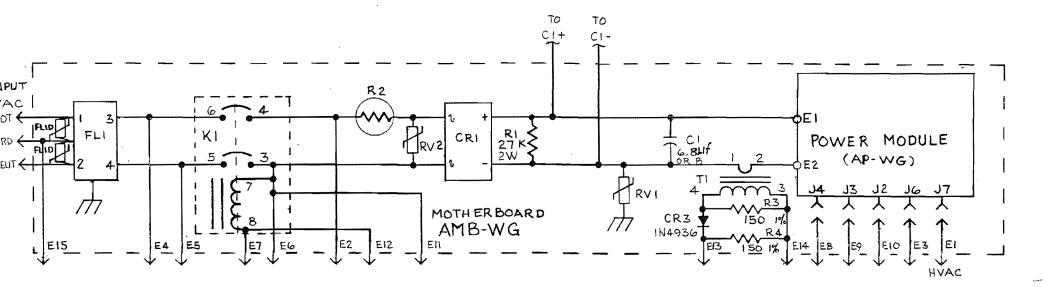

# A. Main Assembly

Refer to the WG Series Main Assembly schematic at the rear of this book. AC input enters the power supply on an input line cord. This is ordinarily 115 volts RMS, 50 - 60 Hz, with a grounded third wire connection. Optional input voltages, as described in the catalog, are available. Power enters through fuse F1 on the rear panel, and then through component FL1, which is an RFI conducted noise filter. The wiring of FL1 physically gounds the third wire to the chassis of the power supply. Power continues to the front panel POWER ON/OFF pushbutton switch, S1. When this switch is in the ON position, the amber pilot light (part of S1) is illuminated, since the low end of the pilot light is returned directly to the low side of the power line. Observe that the "hot" side of the line is also brought to the primary side of transformer T1, and fan B1. These components are not energized since the return to the common side of the line is not yet made. The next action is to close momentary pushbutton switch S2, HV ON. The momentary closure of pushbutton S2 returns components T1, B1, and relay coil K1 to the common side of the power line.

When the coil of contactor/relay K1 is energized, its contacts K1a and K1b, close. This causes K1 coil to go into a selfholding mode, and the HV ON pushbutton S2 may be released. AC power is now applied to the red pilot light (part of S2), as well as to transformer T1, and fan B1. The AC power continues through current limiting resistor R2, to the voltage surge limiting semiconductor CR2, and then to bridge rectifier CR1. The rectified voltage is applied to bleed resistor R1 and capacitor C1, which are in parallel, to develop the main B+ source. The B+ voltage is applied to sub-assembly A3 via terminals 1 and 5 by passing it through surge current sensing sub-assembly A5. Action of these sub-assemblies will be described in subsequent paragraphs.

The balance of the circuitry shown on the main assembly schematic consists essentially of the front panel and rear panel control elements and the interconnecting wiring between the various subassemblies. Included among these components are the following:

R1 and R2 are the ten-turn front panel control potentiometers for current and voltage, respectively. Voltage applied across these potientiometers is derived from the A1 internal reference J1-13, which will be described later. Sliders of the potentiometers are connected to the rear terminals TB1-9 and TB1-6 respectively, as well as being returned internally to J1-14 and

:

J1-11 (on sub-assembly A1) respectively, to be described later. Functions of the terminal connections at TBL on the rear panel are fully described under application information in Section II, Paragraph D, above.

M1 is the front panel kilovoltmeter, and M2 is the front panel milliammeter.

The LED CR2 is the front panel voltage mode indicator, and LED CR1 is the front panel current mode indicator. All of these components will be described subsequently in conjunction with sub-assembly Al.

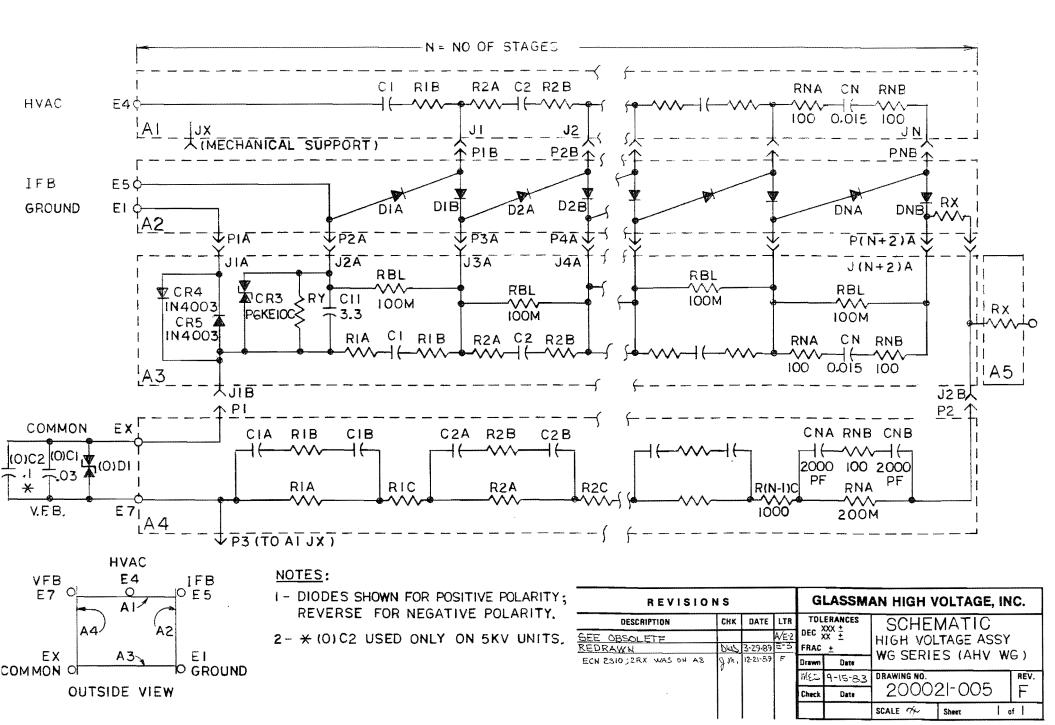

B. High Voltage Assembly

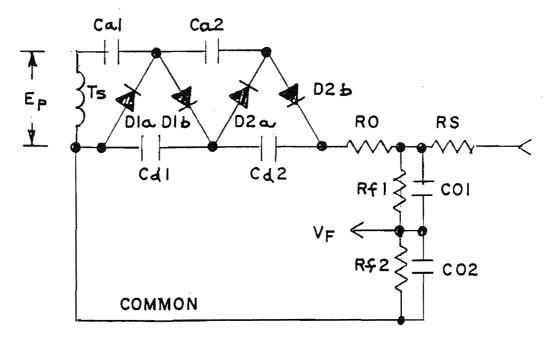

A simplified diagram of the high voltage generating and output circuit is shown above. The circuit is a cascade voltage multiplier, frequently referred to as a Cockroft-Walton generator. For a complete technical discussion of the circuit, numerous articles exist in the literature, of which we have listed several for reference.<sup>1</sup>

A brief description of the multiplier action is as follows: When Ts is at its negative peak, capacitor Cal charges through diode Dla to Ep, the transformer peak voltage. When the transformer polarity reverses, so that its output is positive with respect to common, the transformer voltage, Ep, is then in the same direction as the voltage on the capacitor Cal, and the two voltages add arithmetically. Thus, 2Ep is the driving voltage which charges capacitor Cdl through diode Dlb, and the voltage developed across the capacitor Cdl is equal to 2Ep.

''Factors Controlling the Performance of Cascade Rectifier Circuits"-R.E. Jones, R.T. Waters, Proc IEE, Vol. III, 5, May 64.

Cockcroft-Walton Voltage Multiplier Circuit, Everhart, Lorrain, Rev Sci Instrum, 1953, 24, p.221. Continuing up the multiplier string, and considering again the negative swing of the transformer to Ep, it is easy to see that a net driving voltage of 2Ep is available to charge capacitor Ca2 to 2Ep volts, through diode D2a. Similarly, when the transformer once again drives to its positive peak, Ep, a quick calculation will show that capacitor Cd2 also will charge to a value of 2Ep through diode D2b.

Note that capacitors Cdl and Cd2 are both charged to a voltage 2Ep. This process would continue for any additional voltage multiplier stages. Also note that capacitor Cal is charged to Ep, but capacitor Ca2, and all additional capacitors on this side of the voltage multiplier network, charge to 2Ep. All diodes are subjected to a peak inverse voltage of 2Ep.

Thus, in the voltage multiplier network, it is seen that each stage, consisting of an AC capacitor Ca, a DC capacitor Cd, and two diodes, Dla and Dlb, develops a voltage across the DC capacitor which is equal to twice the peak voltage of the transformer. It is for this reason that the stages of the voltage multiplier network are frequently referred to as voltage doubler stages. The total output voltage of the voltage multiplier is therefore seen to be 2nEp, in which n is the number of doubler stages.

In the above discussion, we have ignored the effects of regulation and component impedances. The voltage 2nEp is the output voltage in the perfect case in which all impedances are zero and the load current is zero. Inherent regulation and ripple can be calculated from the following formulas taken from the reference article by Jones and Waters on the previous page.

> Ripple Volts (p-p) = In(n+1)/2fC Regulation Volts = I(2n /3 + n /4 + n/12)/fC I = DC load current (amperes) n = number of doubler stages f = operating frequency (Hz) C = capacitance per stage (farads)

The schematic shows a resistor Ro, feeding the output feedback network, consisting of resistor divider Col and Co2. The resistor divider generates feedback voltage Vf, which is used to control the regulating loop. Capacitor divider Col and Co2 serve as stabilizing elements for the feedback loop, as well as an output filter capacitor in conjunction with the output resistor Ro. To be specific, the ripple voltage across the voltage multiplying capacitor network consisting of Cdl and Cd2, etc., is attenuated by the RC network consisting of Ro and the series combination of Col and Co2. Rs is a final surge limiting resistor which is a protective device in the event of sudden, severe, overload conditions on the power supply.

The high voltage transformer secondary Ts, which is shown in this schematic, is not physically within the sub-assembly A2. Actually it is a part of the Driver Assembly, A1.

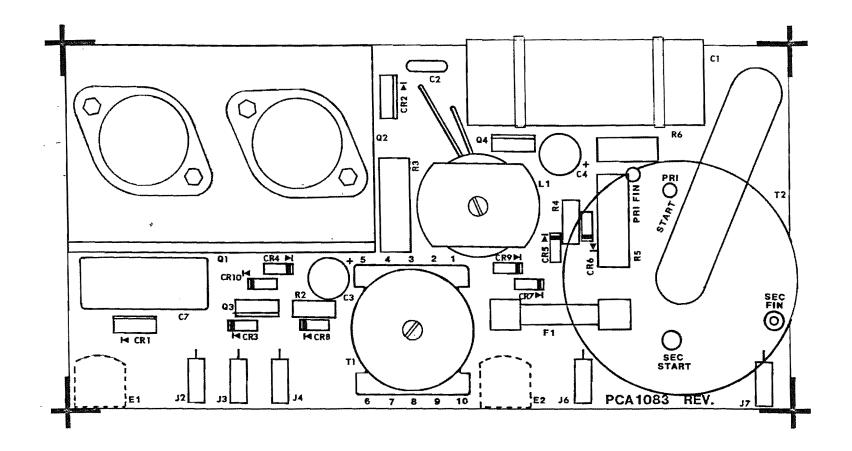

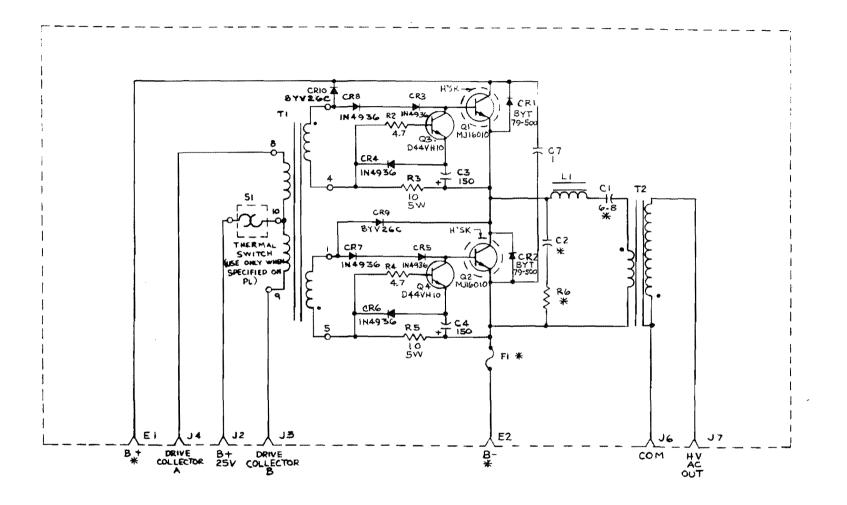

C. <u>Transformer Primary</u>, and Power Transistor Collector Drive Circuitry

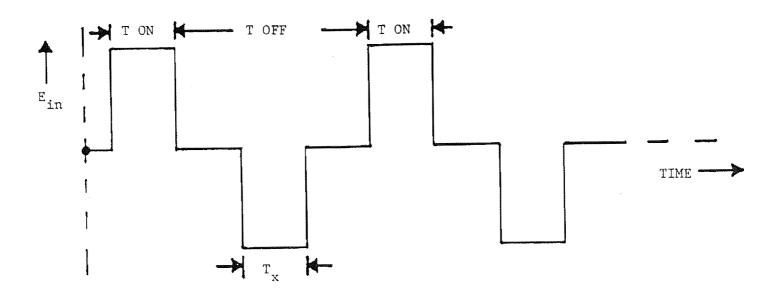

Refer to the Power Module Schematic (AP-WG) at the rear of this manual. This schematic is applicable to the power module shown on the Main Assembly Schematic, which is designated as A3. Observe that the main power transistors Q1 and Q2 are connected in series across the B+/B- power source. The center junction of the two transistors, i.e., the emitter of Q1 and the collector of Q2, are AC coupled through capacitor C1 to the primary of the main high voltage power transformer coil, T2. The drive system, to be described below, is such that Q1 and Q2 are never on simultaneously. Furthermore, the switching system is such that when a transistor is turned on, it is driven to full saturation. Therefore, the circuit may be viewed as a switching system, in which Ql is on for some portion of the cycle that Q2 is off, followed by a period during which both Ql and Q2 are off, then followed by a period during which Q2 is on and Q1 is off. When Q1 is on, the full DC voltage is applied across the series combination of C1 and T2 primary. When Q2 is on, and Q1 is off, a short circuit is applied across the series combination of Cl and T2 primary. By this arrangement, the applied DC B+/B- voltage is "chopped" to a peak-to-peak AC voltage equal to the applied DC voltage, at a frequency which is dependent on the input drive system.

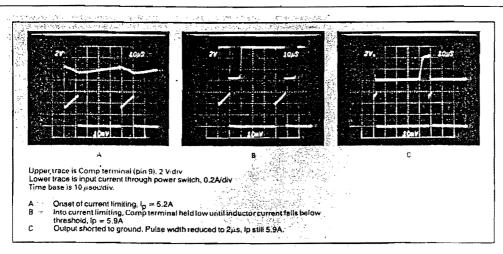

The voltage wave shape shown above is typical for the applied voltage to the base circuitry of Q1 and Q2. The shape shown is

for the voltage of each of the secondary windings of transformer T1, which are applied to the bases of transistors Q1 and Q2. Observe, however, that the two secondary windings are 180° out of phase, so that when a positive pulse is applied to Q1, a negative pulse is simultaneously applied to Q2, and vice versa, Note that the pulse has both a positive and a negative half cycle. However, actual drive to each of the individual transistors Q1 and Q2 occurs only on the positive pulse of the drive transformer wave shape. Thus, during the period T on, let us say that transistor Q1 is on. During the rest of the period until the next positive pulse occurs, the diagram is marked as T off, and transistor Q1 is off. The negative pulse Tx occurs during the off time. It is during this period, Tx, when the other transistor Q2 is actually on.

The pulse width control is such that average voltage applied to the primary of transformer T2 is a function of the on- and offtimes of the input voltage, Ein. As the on-time is reduced, the average voltage applied to the primary of T2 is reduced, and the output voltage is correspondingly and proportionally reduced. Similarly, as the on-time is increased, the output voltage is proportionally increased.

This method of duty cycle control permits the transistors to operate with extreme efficiency, since the transistors are driven to saturation during the period when current is permitted to flow in the particular transistor, and the collector voltage rises only when the primary current is turned off.

Diodes CR1 and CR2 are "catch" clamps, which prevent the transistor collector voltages from rising above the B+/B- level. Capacitor C1 prevents any DC component from flowing in the primary of T2, which prevents DC saturation of the power transformer. The components C2 and R6 serve for dynamic damping during the period when both transistors are off.

The function of Ll is to improve the drive circuit efficiency of the primary system.

We now discuss the base drive circuit of the power transistors. In the discussion which follows, we will use the reference designators for the base drive of transistor Q1. Note that the circuitry is exactly analogous to transistor Q2. When the pulse drive is positive, current flows around the main loop consisting of diode CR3, base to emitter of Q1, and resistor R3. During this period of time, transistor Q1 is driven to saturation, and is turned on. Also during this period, capacitor C3 is charged essentially to the peak pulse voltage of the drive transformer through diode CR4. During the off-time of the pulse, which includes both the period of zero drive voltage, as well as negative pulse voltage, the stored energy in capacitor C3 instantly turns the cutoff transistor Q3 on, providing a sharp cutoff voltage for the main power transistor Q1, reinforcing the removal of base drive current and base charge in transistor Q1. This cutoff circuit is a vital part of the efficient switching of the main power transistors Q1 and Q2.

We now consider the pulse drive applied to the primaries of transformer T1 in the power module. The transformer primary is a tapped winding with the center tap connected to +25 volts via terminal J2. The collector drive windings are designated as CD1 and CD2, and are terminated at terminals J4 and J3, respectively. To see the various interconnections, refer to the Main Assembly schematic. The power module is shown as A3 on the Main Assembly schematic.

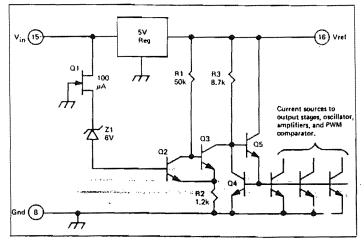

# D. Bias Voltages

Refer again to the Main Assembly schematic and observe that the center-tapped secondary of transformer Tl is connected to the Driver Assembly (A1) through terminals J2-13, -14, and -15. Now refer to the Driver Assembly schematic. J2-14 is connected to common, and J2-13 and -15 are the AC input voltages from the main assembly transformer T1. The AC voltage is applied to the full wave bridge rectifier D16, which develops a pulsating +25V and -25V with respect to common. This is applied to capacitors C21 and C20 to develop filtered +25VDC and -25VDC, respectively. The +25VDC and -25VDC sources are applied to the voltage regulators U8 and U7 to produce regulated +15VDC and -8VDC, respectively. These regulated voltages are applied to the various amplifiers used in the main assembly, to be described below. The regulated +15VDC is applied to the main assembly reference element U6, which develops an extremely stable and well-regulated +10VDC source. Some adjustability is available from this reference by means of adjusting resistor R1. The +15VDC is also used to provide power for the front panel LED pilot lamps, which are VOLTAGE MODE or CURRENT MODE indicators. This function will be described later.

A separate +25VDC source is developed by rectifiers D17, D18, and filter capacitor C38. This source is used to provide B+ voltage for the drive transformer on the power module (A3).

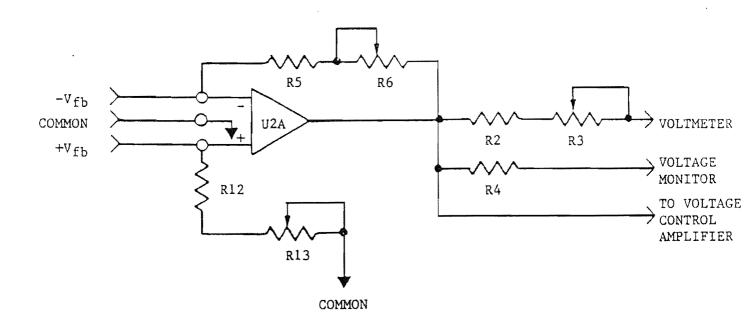

# E. Voltage Feedback Input Amplifier, Polarity Reversal, and Voltage Monitor Circuits.

The above simplified schematic of the Driver Assembly shows the essential components involved in this portion of the circuitry. Consider first the case of a positive high voltage output power supply. In this instance, high voltage feedback current flows in through the terminal marked +Vfb and flows through resistors R12 and R13 (in series) to common, developing a positive voltage across these resistors. R13 is adjusted so that at the rated power supply output voltage, exactly 10 volts is developed across the pair of resistors. This voltage is applied to the noninverting terminal of U2A, which is connected as a follower, with R5 in series with R6, connected between the inverting input terminal and the output terminal of U2A. Thus, the high impedance input configuration is converted to a low impedance output by amplifier U2A. Since the amplifier is connected as a simple follower, the output is exactly equal to the input, and is therefore directly proportional to the high voltage output of the power supply as derived from the voltage feedback current. The output of the amplifier is fed to the front panel voltmeter through resistors R2 and calibrating resistor R3. R3 is used to compensate for any minor inaccuracies in the meter, thereby permitting the meter to be set exactly to full scale for rated output voltage. The amplifier output is also fed to the voltage monitor terminal through resistor R4. R4 is used simply as a protective resistor to protect the power supply in the event that the user inadvertently short circuits or overloads the voltage monitor terminal. Finally, the output of U2A is applied to the

main voltage control feedback amplifier, which will be described below.

When the output of the high voltage power supply is negative, feedback current flows into the terminal marked -Vfb. In this arrangement, U2A acts as an inverting amplifier, in which the non-inverting terminal is connected to common via R12 and R13 in series. The inverting amplifier now forces the inverting terminal of U2A to a virtual ground potential. Thus, current flows from the output of U2A, through resistors R5 and R6 in series, through the inverting input terminal of the amplifier, and finally out through the Vfb terminal to the negative high voltage output, providing the feedback current to the high voltage system. In this polarity, R6 is adjusted so that the output of U2A is exactly 10 volts at the rated output voltage of the power supply.

Therefore, regardless of the high voltage output polarity, the output of the amplifier U2A is always positive and directly proportional to the output voltage. To repeat, the output of U2A is always <u>+10 volts</u> at rated output voltage of the high voltage system, regardless of the polarity. It follows that the voltmeter, voltage monitor, and voltage control amplifiers are the same for this polarity as described above.

- R31 100K D28 I<sub>fb</sub> R49 U3A + 100K D27 COMMON R43 AMMETER + U3B R37 100K R42 CURRENT MONITOR R45 R46 TO CURRENT 100K 348K CONTROL R50 AMPLIFIER 49.9K

- F. <u>Current Feedback Input Amplifier</u>, Polarity Reversal, and Current Monitor Circuits

The above simplified schematic of the Driver Assembly shows the basic elements used in the current feedback input amplifier and

the technique used to automatically sense the specific polarity of the power supply output voltage. The terminal marked Ifb is actually a voltage source derived from the high voltage assembly when load current flows through the sensing resistor. Rx, which was described above in Paragraph B. The polarity of the voltage developed across Rx is either positive or negative, depending on whether the high voltage output polarity is negative or positive, respectively. Referring to the simplified schematic of the high voltage assembly in Paragraph B, note that the high voltage diodes are drawn for a positive high voltage polarity condition. In this case, current flows from ground or common through resistor Rx into the high voltage diodes Dla, Dlb, D2a, and D2b to the high voltage output terminal. Thus, the voltage developed at terminal Ifb is negative with respect to ground. Refer again to the above simplified schematic. Ιf the input source voltage is negative, observe that the output of amplifier U3B is positive, so that current flows through resistors R46 and R45 in series, to resistor R37, and then into the current source. The design is such that R46 is adjusted to make the series combination of resistors R46 and R45 exactly four times the value of resistor R37. Thus, if the output of U3B is to be the design value of 10 volts, the drop across the current sensing resistor will be -2.5 volts, i.e., a four-to-one ratio. Observe that the output of amplifier U3A must supply current through D28 to the virtual ground inverting input terminal of U3A, and will feed current through R31 to the current source. Also note that since D27 is reverse biased, no current flows through R50 and R49, since there is no potential difference across these resistors.

For the other polarity, the Ifb terminal will be +2.5 volts at rated load current. In this case, current flows from the source through R31 and through R37 to the virtual ground at the inverting input terminals of U3A and U3B. Current in R31 is sinked through resistor R49 and diode D27 to amplifier output U3A. In this case, D28 is reverse biased. Now the output of U3B is again positive and provides the necessary current through R45 and R46 to produce the virtual ground at the inverting input terminal of U3B. The two components of current, i.e., the one through R37 and the one through the series combination of R45 and R46, exit the inverting input junction terminal of U3B through resistor R50 and are also sinked by the output terminal of amplifier U3A.

It is thus seen that the output of U3B is designed to be +10 volts for either a positive or a negative current source input of 2.5 volts from the high voltage current feedback system. The output voltage of U3B is applied to the front panel milliammeter through resistors R43 and R44 in series, R44 being used as an adjustment to calibrate for any meter inaccuracies. The output voltage is also applied to the current monitor terminal through R42. The function of R42 is to prevent overload of the amplifier in the inadvertent short circuiting or overloading of the current monitor terminal. Finally, the output of U3B is applied to the current control amplifier to be described on the following page.

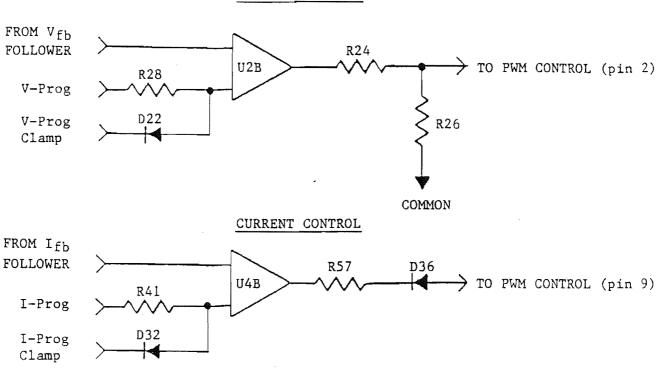

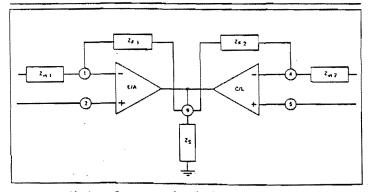

# G. <u>Feedback Control Amplifiers and Programming</u>, Voltage and <u>Current Regulators</u>

The simplified schematic above shows the basic circuit elements of the voltage control and current control amplifier systems. Complete details for these circuits can be found by referring to the Driver Assembly schematic at the rear of this manual. The schematic reference designators shown in the above sketches correspond to the equivalent parts on the complete schematic. Only the key components are included in these sketches. The two circuits, voltage and current control, are quite analogous. We will describe only the voltage control amplifier in the following discussion. The voltage program and current program signals may be selected optionally by the user in several different manners, all of which have been described previously in Section II, Paragraph D.

The feedback loop is closed at the input of control amplifier U2B in a conventional comparator configuration. The programming voltage signal is applied through resistor R28 to the noninverting input terminal of the amplifier. The output information from the voltage feedback follower amplifier is applied to the inverting input terminal of the control amplifier.

VOLTAGE CONTROL

The circuit is similar to most closed loop configurations. The input signal, obtained as a portion of the reference voltage and referred to as programming voltage, is applied to one input of the control amplifier. The loop then drives the output voltage of the power supply to a level such that the signal returned from the feedback divider and follower amplifiers described in an earlier paragraph, and applied to the other input of the control amplifier, "nulls" the amplifier and balances the applied program voltage. The output of the control amplifier is used to control the pulse width modulator main driver, to be described below.

D22 is connected from the positive amplifier input terminal (after the voltage programming input resistor) to the voltage program clamp. Normally, this connection is made to the slider of the front panel ten-turn voltage control. Thus, if an external programming signal is applied to the power supply, it can be clamped by the front panel ten-turn control, thereby permitting this control to be used as an overvoltage limit. In other words, the setting of the front panel voltage adjust clamps the remote program signal, and limits the output voltage to a level corresponding to the setting on the front panel control.

In the current control amplifier, diode D36 in the output is the "crossover" element which permits the power supply to automatically change from a voltage mode to a current mode of operation. Thus, as long as the current programming input signal is greater than the actual output current feedback information, the output of amplifier U4B is "high", and diode D36 is back biased, and decoupled. When the load current, and the subsequent feedback follower information reaches the level of the current program signal, U4B amplifier goes into its dynamic range. Diode D36 is forward biased and the pulse width modulator control overrides that of the voltage amplifier.

Not shown on the simplified sketches above are the numerous protective diode clamps required to protect the circuitry under transient conditions. Also not shown is the automatic gain circuit, consisting of transistor Q3 and photocell U5. The gain is increased as the power supply load current increases, to achieve fast loop response and an improved ripple characteristic. The gain is reduced at light load, to stabilize the feedback loop under these operating conditions.

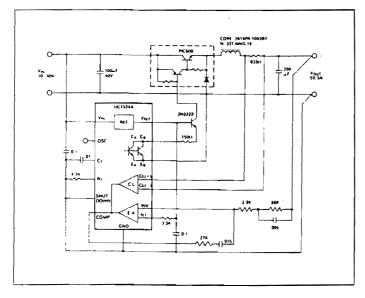

# H. Pulse Width Modulator

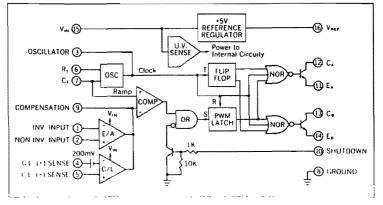

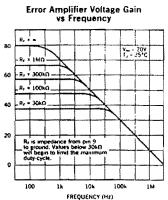

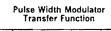

Ul on the Driver Assembly is an integrated circuit which provides all the controls required to establish the pulse width modulator drive system. The next few pages of this instruction manual contain copies of the manufacturer's data sheets for the part used in this power supply. It is recommended that if this part needs replacement, the same manufacturer and manufacturer's part number be used. Any substitutions should be checked with the Glassman Engineering Department.

# LINEAR INTEGRATED CIRCUITS Advanced Regulating Pulse Width Modulators

#### FEATURES

- Fully interchangeable with standard UC1524 family

- Precision reference internally trimmed to ±1%

- High-Performance current limit function

- Under-voltage lockout with hysteretic turn-on

- · Start-up supply current less than 4mA

- Output current to 200mA

- · 60V output capability

- Wide common-mode input range for both error and current limit amplifiers

- PWM latch insures single pulse per period

- 200ns shutdown through PWM latch

- · Guaranteed frequency accuracy

#### DESCRIPTION

The UC1524A family of regulating PWM ICs has been designed to retain the same highly versatile architecture of the industry standard UC1524 (SG1524) while offering substantial improvements to many of its limitations. The UC1524A is pin compatible with "non-A" models and in most existing applications can be directly interchanged with no effect on power supply performance. Using the UC1524A, however, frees the designer from many concerns which typically had required additional circuitry to solve.

UC1524A UC2524A

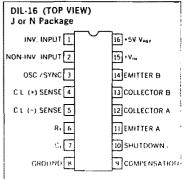

The UC1524A includes a precise 5V reference trimmed to ±1% accuracy, eliminating the need for potentiometer adjustments; an error amplifier with an input range which includes 5V, eliminating the need for a reference divider; a current sense amplifier useful in either the ground or power supply output lines; and a pair of 60V, 200mA uncommitted transistor switches which greatly enhance output versatility.

An additional feature of the UC1524A is an under-voltage lockout circuit which disables all the internal circuitry, except the reference, until the input voltage has risen to 8V. This holds standby current low until turn-on, greatly simplifying the design of low power, off-line supplies. The turn-on circuit has approximately 600mV of hysteresis for jitterfree activation.

Other product enhancements included in the UC1524A's design include a PWM latch which insures freedom from multiple pulsing within a period even in noisy environments and a shutdown circuit feeding directly to the latch which will disable the outputs within 200ns. The oscillator circuit of the UC1524A is usable beyond 500kHz and is now easier to synchronize with an external clock pulse.

The UC1524A is packaged in a hermetic 16-pin DIP and is rated for operation from -55°C to +125°C. The UC2524A and UC3524A are available in either ceramic or plastic packages and are rated for operation from -25°C to +85°C and 0°C to 70°C, respectively.

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage (V <sub>IN</sub> )           |                |

|---------------------------------------------|----------------|

| Collector Supply Voltage (Vc)               |                |

| UC1524A, UC2524A                            |                |

| UC3524A                                     |                |

| Output Current (Each Output)                |                |

| Reference Output Current                    |                |

| Oscillator Charging Current                 |                |

| Power Dissipation at T <sub>A</sub> = +25°C | 1000mW         |

| Derate above +50°C                          | 10mW/°C        |

| Power Dissipation at T <sub>c</sub> = +25°C |                |

| Derate for Case Temperature above +25°C     | 16mW/°C        |

| Operating Temperature Range                 | 55°C to +125°C |

| Storage Temperature Range                   |                |

| Lead Temperature (Soldering, 10 seconds)    |                |

#### BLOCK DIAGRAM

#### CONNECTION DIAGRAM

#### UC1524A UC2524A UC3524A

**ELECTRICAL CHARACTERISTICS** (Unless otherwise stated, these specifications apply for  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$  for the UC1524A,  $-25^{\circ}C$  to  $+85^{\circ}C$  for the UC2524A, and 0°C to  $+70^{\circ}C$  for the UC3524A;  $V_{IN} = V_C = 20V$ .)

|                                    |                                                     |      | UC1524A<br>UC2524A<br>UC2524A |      |      | A    |      |                                                                                                                                                                                      |

|------------------------------------|-----------------------------------------------------|------|-------------------------------|------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                          | TEST CONDITIONS                                     | MIN. | TYP.                          | MAX. | MIN. | TYP. | MAX. | UNITS<br>V<br>V<br>MA<br>MA<br>V<br>W<br>MV<br>W<br>W<br>W<br>MV<br>MV<br>MV<br>MV<br>MV<br>MV<br>MV<br>KHz<br>KHz<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>MV |

| Turn-on Characteristics            |                                                     |      |                               |      |      |      |      | ·····                                                                                                                                                                                |

| Input Voltage                      | Operating range after Turn-on                       | 8    |                               | 40   | 8    |      | 40   | v                                                                                                                                                                                    |

| Turn-on Threshold                  |                                                     | 6    | 7.5                           | 8.5  | 6    | 7.5  | 8.5  | v                                                                                                                                                                                    |

| Turn-on Current                    | V <sub>IN</sub> = 6V                                |      | 2.5                           | 4    |      | 2.5  | 4    | mA                                                                                                                                                                                   |

| Operating Current                  | V <sub>IN</sub> = 8 to 40V                          |      | 5                             | 10   |      | 5    | 10   | mA                                                                                                                                                                                   |

| Turn-on Hysteresis*                |                                                     |      | 0.6                           |      |      | 0.6  |      | v                                                                                                                                                                                    |

| Reference Section                  |                                                     |      |                               |      | d    |      |      |                                                                                                                                                                                      |

| Output Voltage                     | T, = 25°C                                           | 4.95 | 5.00                          | 5.05 | 4.90 | 5.00 | 5.10 | V                                                                                                                                                                                    |

| Line Regulation                    | V <sub>IN</sub> = 10 to 40V                         |      | 10                            | 20   |      | 10   | 30   | mV                                                                                                                                                                                   |

| Load Regulation                    | 1 <sub>L</sub> = 0 to 20mA                          |      | 20                            | 50   |      | 20   | 50   | m٧                                                                                                                                                                                   |

| Temperature Stability*             | Over Operating Range                                |      | 20                            | 50   |      | 20   | 50   | m٧                                                                                                                                                                                   |

| Short Circuit Current              | $V_{REF} = 0, T_{i} = 25^{\circ}C$                  |      | 80                            | 100  |      | 80   | 100  | mA                                                                                                                                                                                   |

| Output Noise Voltage*              | $10hz \le f \le 10kHz, T_i = 25^{\circ}C$           |      | 40                            |      |      | 40   |      | μVrms                                                                                                                                                                                |

| Long Term Stability*               | T <sub>i</sub> = 125°C, 1000 Hrs.                   |      | 20                            | 50   |      | 20   | 50   | mV                                                                                                                                                                                   |

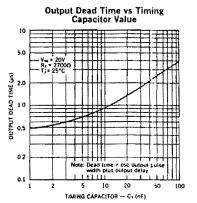

| Oscillator Section (Unless otherwi | se specified, $R_T = 2700\Omega$ , $C_T = 0.01$ mfd | )    |                               |      |      |      |      |                                                                                                                                                                                      |

| Initial Accuracy                   | T, = 25°C                                           | 40   | 43                            | 46   |      | 43   |      | kHz                                                                                                                                                                                  |

| Temperature Stability*             | Over Operating Temperature Range                    |      | 1                             | 2    |      | 1    | 2    | %                                                                                                                                                                                    |

| Minimum Frequency                  | $R_T = 150k\Omega$ , $C_T = 0.1 mfd$                |      |                               | 120  |      |      | 120  | Hz                                                                                                                                                                                   |

| Maximum Frequency                  | $R_{r} = 2.0 k\Omega, C_{r} = 470 pF$               | 500  |                               |      | 500  |      |      | kHz                                                                                                                                                                                  |

| Output Amplitude*                  | T <sub>1</sub> = 25°C                               |      | 3.5                           |      |      | 3.5  |      | v                                                                                                                                                                                    |

| Output Pulse Width*                | T <sub>i</sub> = 25°C                               |      | 0.5                           |      | 1    | 0.5  |      | μ5                                                                                                                                                                                   |

| Ramp Peak                          |                                                     | 3.3  | 3.5                           | 3.7  | 3.3  | 3.5  | 3.7  | V                                                                                                                                                                                    |

| Ramp Valley                        |                                                     | 0.7  | 0.9                           | 1.0  | 0.7  | 0.9  | 1.0  | V                                                                                                                                                                                    |

| Error Amplifier Section (Unles oth | erwise specified, V <sub>CM</sub> = 2.5V)           |      |                               |      |      | -    |      |                                                                                                                                                                                      |

| Input Offset Voltage               |                                                     |      | 0.5                           | 5    |      | 2    | 10   | ۳n۷                                                                                                                                                                                  |

| Input Bias Current                 |                                                     |      | 1                             | 5    |      | 1    | 10   | μA                                                                                                                                                                                   |

| Input Offset Current               |                                                     |      | .05                           | 1    |      | 0.5  | 1    | μA                                                                                                                                                                                   |

| Common Mode Rejection Ratio        | V <sub>CM</sub> = 1.5 to 5.5V                       | 60   | 75                            |      | 60   | 75   |      | dB                                                                                                                                                                                   |

| Power Supply Rejection Ratio       | V <sub>IN</sub> = 10 to 40V                         | 50   | 60                            |      | 50   | 60   |      | dB                                                                                                                                                                                   |

| Output Swing                       | Minimum Total Range                                 | 0.5  |                               | 5.0  | 0.5  |      | 5.0  | V                                                                                                                                                                                    |

| Open Loop Voltage Gain             | $\Delta V_0 = 1$ to 4V, $R_L \ge 10$ Meg $\Omega$   | 72   | 80                            |      | 60   | 80   |      | dB                                                                                                                                                                                   |

| Gain-Bandwidth*                    | $T_1 = 25^{\circ}C, A_V = 0dB$                      |      | 3                             |      |      | 3    |      | MHz                                                                                                                                                                                  |

\* These parameters are guaranteed by design but not 100% tested in production.

ł

#### UC1524A UC2524A UC3524A

|                                    |                                                              | }    | UC1524<br>UC2524 |           |       |         |           |        |  |

|------------------------------------|--------------------------------------------------------------|------|------------------|-----------|-------|---------|-----------|--------|--|

| PARAMETER                          | TEST CONDITIONS                                              | MIN. | TYP.             | MAX.      | MIN.  | TYP.    | MAX.      | UNITS  |  |

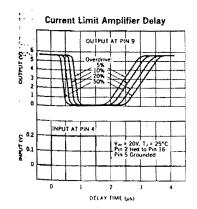

| Current Limit Amplifier (Unless ot | herwise specified, Pin 5 =0V)                                |      |                  |           |       |         | -         |        |  |

| Input Offset Voitage               | T <sub>i</sub> = 25*C, E/A Set for Maximum Output            | 190  | 200              | 210       | 180   | 200     | 220       | m۷     |  |

| Input Offset Voltage               | Over Operating Temperature Range                             | 180  |                  | 220       | 170   |         | 230       | mV     |  |

| Input Bias Current                 |                                                              |      | -1               | -10       |       | -1      | -10       | μA     |  |

| Common Mode Rejection Ratio        | V(Pin 5) = -0.3V to +5.5V                                    | 50   | 60               |           | 50    | 60      |           | dB     |  |

| Power Supply Rejection Ration      | V <sub>IN</sub> = 10 to 40V                                  | 50   | 60               |           | 50    | 60      | 1         | dB     |  |

| Output Swing                       | Minimum Total Range                                          | 0.5  |                  | 5.0       | 0.5 · |         | 5.0       | V      |  |

| Open Loop Voltage Gain             | $\Delta V_{o} = 1$ to 4V, $R_{L} \ge 10 \text{ Meg } \Omega$ | 70   | 80               |           | 70    | 80      |           | dB     |  |

| Delay Time*                        | Pin 4 to Pin 9, ΔV <sub>IN</sub> = 300mV                     |      | 300              |           |       | 300     |           | ns     |  |

| Output Section (Each Output)       |                                                              |      |                  |           |       |         |           |        |  |

| Collector Emitter Voltage          | $t_c = 100\mu A$                                             | 60   | 80               |           | 50    | 80      |           | V      |  |

| Collector Leakage Current          | V <sub>CE</sub> = 50V                                        |      | .1               | 20        |       | .1      | 20        | μA     |  |

| Saturation Voltage                 | lc = 20mA<br>lc = 200mA                                      |      | .2<br>1          | .4<br>2.2 |       | .2<br>1 | .4<br>2.2 | V<br>V |  |

| Emitter Output Voltage             | I <sub>E</sub> = 50mA                                        | 17   | 18               |           | 17    | 18      |           | V      |  |

| Rise Time*                         | T <sub>i</sub> = 25°C, R = 2Κ Ω                              |      | 200              |           |       | 200     |           | ns     |  |

| Fall Time*                         | T <sub>j</sub> = 25°C, R = 2K Ω                              |      | 100              |           |       | 100     | [         | ns     |  |

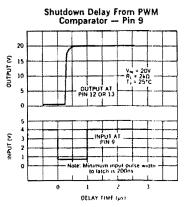

| Comparator Delay*                  | T <sub>i</sub> = 25°C, Pin 9 to Output                       |      | 300              |           |       | 300     |           | ns     |  |

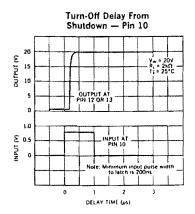

| Shutdown Delay*                    | T <sub>j</sub> = 25°C, Pin 10 to Output                      |      | 200              |           |       | 200     |           | ns     |  |

| Shutdown Threshold                 | $T_{i} = 25^{\circ}C, R_{c} = 2K \Omega$                     | 0.5  | .7               | 1.0       | 0.5   | .7      | 1.0       | v      |  |

ELECTRICAL CHARACTERISTICS (Unless otherwise stated, these specifications apply for T<sub>A</sub> = -55°C to +125°C for the UC1524A, -25°C to +85°C for the UC2524A, and 0°C to +70°C for the UC3524A; V<sub>IN</sub> = V<sub>c</sub> = 20V.)

\* These parameters are guaranteed by design but not 100% tested in production.

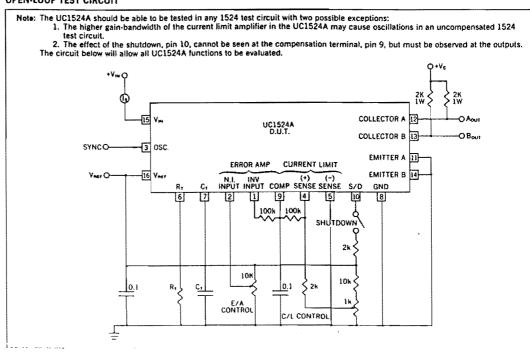

#### **OPEN-LOOP TEST CIRCUIT**

#### UC1524A UC2524A UC3524A

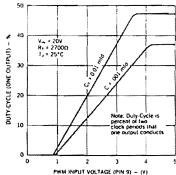

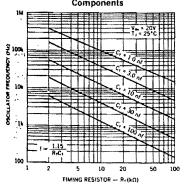

Oscillator Frequency vs Timing Components

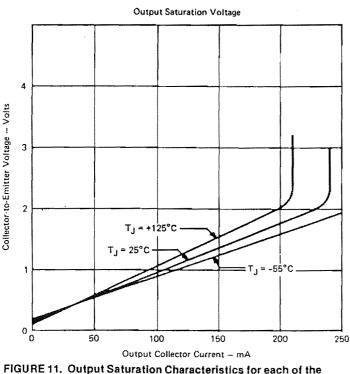

Output Saturation Voltage

# Recent Advances in IC Switching Power Supply Controllers Reach New Performance Levels While Reducing System Costs

by Robert Mammano, Vice President of Engineering Unitrode Integrated Circuits Corporation

High frequencies; more output power, easier interfacing, better fault sensing, lower internal power losses, greater accuracy, increased predictability, and more selfcontained features: These are the improvements power supply designers have been demanding of IC technology in order to reduce their overall system costs. Efforts toward accomplishing these goals have been directed both toward improving existing products as well as developing new devices to significantly extend the state of the art. This article introduces the results of this activity by describing a newly redesigned IC controller and illustrating its benefit to the power supply engineer.

Building a successful switching power supply has always represented a battle against cost. It was the high cost of implementing switching technology which most often dictated linear power supplies in the past. While tremendous strides have been made in improving performance and reducing costs of components, the battle is far from over. Every time a designer sits down to develop a new power system, his major task is usually not how to solve a technical problem but how to implement the design in a cost-effective manner. The designer only wins if his resultant power supply is competitive in the marketplace, regardless of whether it's a stand-alone power source or part of a larger system.

The introduction of integrated circuit pulse-width modulator (PWM) controllers has made significant contribution to lowering switching power supply costs by reducing much of the regulator circuit complexity to a single chip. There have been so many developments in this area that one might suspect all potential gains have already been achieved. However, open any switching power supply on the market today and one will still see a fairly large P.C. board containing a multitude of discrete control components. Although significant improvements have been made, the ultimate IC controller chip has yet to be defined.

# IC CONTROLLERS

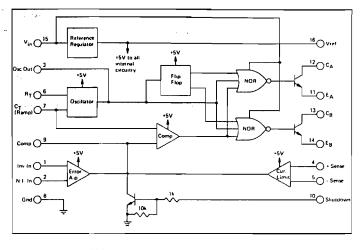

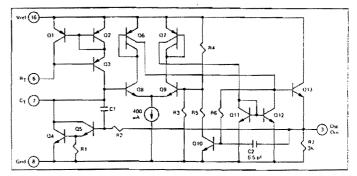

The application of IC technology to the switching power supply began with the introduction of the SG1524 in 1976. This device, whose block diagram is shown in Figure 1, was the first IC to implement all the control blocks necessary for a wide range of PWM power systems. Its straightforward approach to the classic PWM architecture gave it wide acceptance, and it has become the most widely used IC controller today.

NEDRONVEDRIALISTERN

FIGURE 1. The UC1524 Pulse Width Modulator Block Diagram

Even though the 1524 has gained great acceptance and engineers have praised its versatile and easy to understand architecture, they have many times cursed the simplistic, or idealistic, ways its individual blocks were implemented. While one would assume, at first glance, that all control functions necessary for most power supply applications are contained within the 1524, in the real world of practical power systems, additional circuitry is required to interface with the rest of the system, to protect against different types of fault conditions, to adjust for inaccuracies, or to improve control during power sequencing.

The TL494 was introduced to provide better analog instrumentation for voltage and current sensing and increased output power, and it won many converts. But it also suffered from a need for external support and protection circuitry to incorporate it within a practical power supply.

A second generation circuit, the SG1525A was developed for more optimum utilization in specialized applications. This part was the first IC controller circuit to incorporate a trimmed 1% reference and a PWM latch for jitter-free operation in noisy environments. The 1525A also featured totem-pole outputs for turn-off, as well as turn-on commands. While this improved interfacing in some applications, it sacrificed some of the flexibility offered by the 1524s uncommitted outputs.

A third generation circuit, the SG1526, provided further improvements such as more internal protection circuitry and a wide-range current limiting amplifier at the cost of considerable complexity and increased internal power losses.

# **Recent Advances in IC Switching**

(continued from page 14)

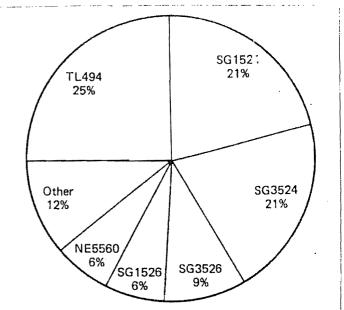

Another choice offered power supply designers was the NE5560, whose major advantage was the capability for input voltage sensing for constant volt-second operation. While greatly improving line regulation, this device offered only a single, low-current output.

With the availability of all the above devices, plus several other "also-rans", design engineers now have a wide range of choices from which to select the IC which results in the lowest system cost for their particular application. In an attempt to understand more about these decisions; an independent survey was conducted last October, with 122 individuals from 97 different companies, representing both power supply manufacturers and captive design groups within OEM companies. The survey asked, among other questions, which is the preferred IC controller chip. The results of this survey are shown in Figure 2.

With some 42% of the users preferring the 1524 family, it seemed appropriate to take a closer look at the reasons. A key factor in the 1524s acceptance appeared to be the wide versatility offered by its easy-to-understand PWM architecture. From this study it became apparent that a new design, which would improve many of the 1524's individual functions by making them more predictable and easier to apply, while retaining the same architecture, could be a winner. Thus, Unitrode undertook this task. The result is the UC1524A.

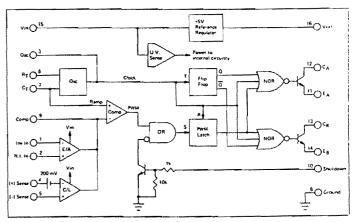

# THE UC1524A PWM CONTROLLER

A design goal set for the UC1524A was that it not only retain the same architecture but keep the same pin configuration as the 1524 and function equal to or better than the 1524 in most existing applications. In this way, engineers who were familiar with the 1524 could easily understand and evaluate the UC1524A. Performance improvements had to be significant, particularly in reducing the need for discrete support circuitry, so there would be a cost advantage in using the UC1524A in new designs. The block diagram of the UC1524A is shown in Figure 3, which, by intent, looks very similar to the diagram of Figure 1.

The list of improvements, however, is considerable and includes the following:

•The 5V reference is now internally trimmed to  $\pm 1\%$  accuracy, eliminating the need for potentiometer adjustments.

•The error amplifier's input range now extends beyond 5V, eliminating the need for a pair of dividers and their attendant tolerances.

•A high-gain, wide-band, current sense amplifier has been included which is useful for either linear or pulse-bypulse current limiting in the ground or power supply output lines.

•An under voltage lockout circuit has been added which disables all the internal circuitry except the reference until the input voltage has risen to 8V. This holds standby current low until turn-on, greatly simplifying the design of low-power, off-line converters. There is approximately 600mV of hysteresis included for jitter-free activation.

•A PWM latch has been added insuring freedom from

16 POWERCONVERSION INTERNATIONAL

FIGURE 2. Results of a 1981 Survey of Control IC Usage by Part Number Shown by Percent of Engineer Responses

FIGURE 3. The UC1524A Block Diagram follows the same Architecture as the UC1524 but with Several Significant Differences

multiple pulsing within a period, even in noisy environments. In addition, the shutdown circuit feeds directly to this latch which will disable the outputs within 200nsec of activation.

•The oscillator circuit is usable to frequencies beyond 500kHz and is easier to synchronize with an external clock pulse.

•The power capability of the output switches has been boosted by doubling the current capability to 200mA and increasing the voltage rating to 60V.

An understanding of some of these improvements is necessary for ease in application and will now be discussed in greater detail.

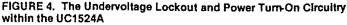

# INTERNAL POWER TURN-ON CIRCUIT

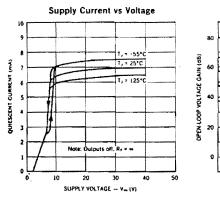

The undervoltage lockout and turn-on hysteresis circuit is shown in Figure 4. This circuit requires approximately 2V for activation; and, since nothing else will turn on without at least 3V of supply voltage, lockout is assured. When  $V_{in}$  rises above 2V, R1 begins to conduct saturating Q3 and holding the base of Q5 too low to allow any of the current sources to conduct. The current through R3 flows through Q3 and R2, developing a 600mV drop across R2 when Vref reaches 5V. At this level, the only current flowing is that used by the reference regulator and R1 and R3, a total of approximately 2.5mA at turn-on threshold.

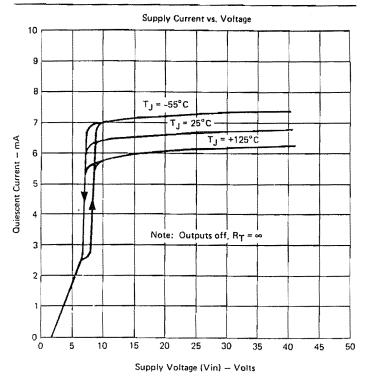

FIGURE 5. Supply Current for the UC1524A vs Input Voltage

When the input voltage reaches approximately 8V, Z1 begins to conduct turning on Q2 which turns off Q3 and allows the current sources to activate. Since the current through Q2 is much less than through Q3, the voltage across R2 drops providing positive feedback. This gives about 600mV of hysteresis. This circuit, of course, works in reverse at turn off, insuring that the outputs can only operate when the supply is adequate for fully predictable operation. Figure 5 shows the relationship between quiescent current and input voltage. Designers should find this low current start-up characteristic quite advantageous for off-line, primary-side control with bootstrapped operation after turn on.

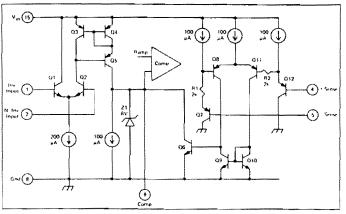

# A NEW CURRENT LIMIT AMPLIFIER

Since the outputs of the current limit amplifier and the voltage-sensing error amplifier are summed at the PWM comparator input, they should be examined together as shown in Figure 6. Since the error amplifier, consisting of transistors Q1 through Q5, must have the lowest priority in controlling the PWM, its output must be easily overruled by current faults or other programming functions, such as soft-start, which would hold pin 9 low. Therefore, a transconductance amplifier similar to that used in the earlier 1524 was again applied to the 1524A with one exception: It is now powered by V<sub>in</sub> instead of Vref, so that the input common-mode range extends to within 2V of either rail. Zener diode, Z1, is used on the output to keep the input level to the PWM comparator below 6V.

The error amplifier's output can be considered a  $100\mu$ A current source or sink (0 -  $200\mu$ A source with  $100\mu$ A constant sink). When the current limit circuit activates, Q6 turns on and can easily pull down pin 9 even though the error amplifier would nominally be calling for a high output at this point.

The current limit circuit consists of Q6 through Q12. Its differential PNP input stage gives it a common mode range extending from 300mV below ground to within 2V of  $V_{in}$ . Its threshold, or offset, of 200mV is established by the 100 $\mu$ A current source through R1, with R2 added to null out the effect of any base current from Q8.

This current sensing block within the UC1524A can actually be used either as a linear amplifier or as a comparator. The open loop small-signal gain is approximately 80dB while its transition delay with 10% overdrive is 600nsec. This can be decreased substantially with additional overdirve. Use of the current sensing block as a comparator is usually preferred from a systems standpoint, since it does not have to be compensated and pin 9 can be dedicated solely to error amplifier compensation. Under this condition, a current signal over the threshold level will pull pin 9 low, terminating the output signal. Recovery is determined by the 100µA pull-up current from the error amplifier in conjunction with any capacitance which may be present on pin 9.

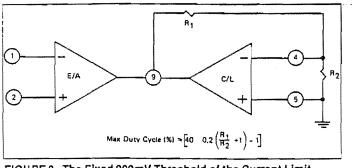

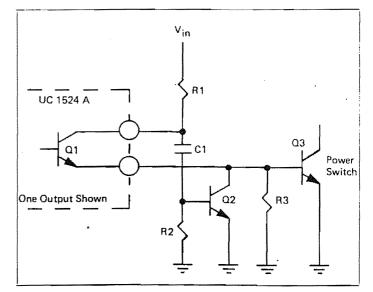

When the current limit circuit is used as a linear amplifier, stablization is performed by feedback to the inverting input (pin 4) or by capacitance from pin 9 to ground as shown in Figure 7.

An additional feature of this circuit is its capability to perform as a duty-cycle limiting circuit in the configuration shown in Figure 8. If R1 is made 100k, there will be minimal effect upon the error amplifier gain.

(continued on following page)

# **Recent Advances in IC Switching**

(continued from preceding page)

FIGURE 8. The Fixed 200mV Threshold of the Current Limit Amplifier can be Multiplied to form a Duty-Cycle Clamp, or Dead-Band Control

In current limiting, to achieve the fastest responding pulse-by-pulse control, consideration should be given to the use of the shutdown terminal on pin 10. While the input threshold of this circuit is not as accurately controlled, has a negative temperature coefficient of  $-2mV/^{\circ}C$  and is internally ground referenced; it does feed directly into the PWM latch with only 200nsec delay from activation of pin 10 to shutdown of the outputs.

# PWM COMPARATOR AND LATCH

The PWM latch insures only a single pulse is allowed to the appropriate output stage within each. period: The latch is reset with the oscillator clock pulse which also serves to blank the outputs. Thus, although the latch is reset at the start of the oscillator clock pulse, it is the termination of the clock pulse which initiates output conduction. The output then stays on until the latch is set, either by a signal from the

|                 | ななななななな                                                                          |

|-----------------|----------------------------------------------------------------------------------|

|                 |                                                                                  |

|                 |                                                                                  |

|                 |                                                                                  |

|                 |                                                                                  |

| Lower<br>Middle | <ul> <li>Current sense input, 200 mV/div</li> <li>Comp output, 5V/div</li> </ul> |

| Top<br>Time     | <ul> <li>Output, 10V/div</li> <li>1 μsec/div</li> </ul>                          |

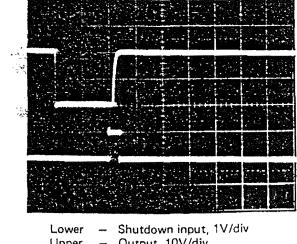

FIGURE 10. Typical Turn-Off Response from both the Current Sense and Shutdown Inputs

PWM comparator or from a shutdown command from pin 10. Once the latch is set, it will hold the output off for the duration of the period.

There are several significant advantages to this circuit. First, the latch completely eliminates multiple outputs of the PWM comparator because of noise or ringing on the output of the error amplifier causing multiple crossings of the ramp signal. Second, current limiting can now be performed much more rapidly without instability. Without a latch, significant integration is needed to maintain a turn-off signal after the outputs have turned off. Finally, any instabilities which might potentially be present in the voltage or current loops, or the shutdown signal from pin 10, will cause much less stress on the output stages, since only two transitions through the high-dissipation active region can be made during each period

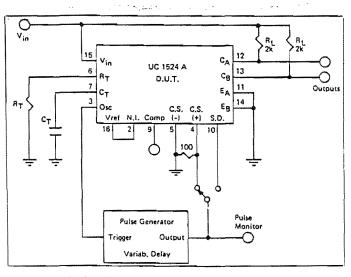

FIGURE 9. Evaluating the Turn-Off Delays of the UC1524A with the aid of a Triggerable Pulse Generator with Variable Delay

The performance of this portion of the UC1524A can be evaluated using a triggerable pulse generator with a variable delay, setup as shown in Figure 9.  $R_T$  and  $C_T$  are selected for the desired operating frequency. The clock triggers the pulse generator, and the delay is adjusted so the generator output occurs during the PWM period. The

Upper – Output, 10V/divTime – 1  $\mu$ sec/div

20 POWERCONVERSION INTERNATIONAL

output pulse width must be at least 200nsec and the amplitude higher than the threshold of the UC1524A input being evaluated. Typical waveform photographs are shown in Figure 10.

# HIGHER POWER OUTPUT SWITCHES

With the higher current and voltage rating of the UC1524A's output switches, significant economies can now be achieved in interfacing with higher power devices. For low power requirements, a broader range of applications may now be served by the 1524A itself without additional discrete output devices. Regardless of the power supply requirements, more current and voltage from the UC1524A will ease the design tradeoffs. Even with higher current and voltage, the UC1524A offers fast response time. Each output stage contains an anti-saturation network to keep the output transistors out of hard saturation. Although this adds somewhat to the saturation voltage, it is more than offset by the benefits in reducing turn-off delay. Saturation voltage as a function of current is shown in Figure 11.

UC1524A's Outputs